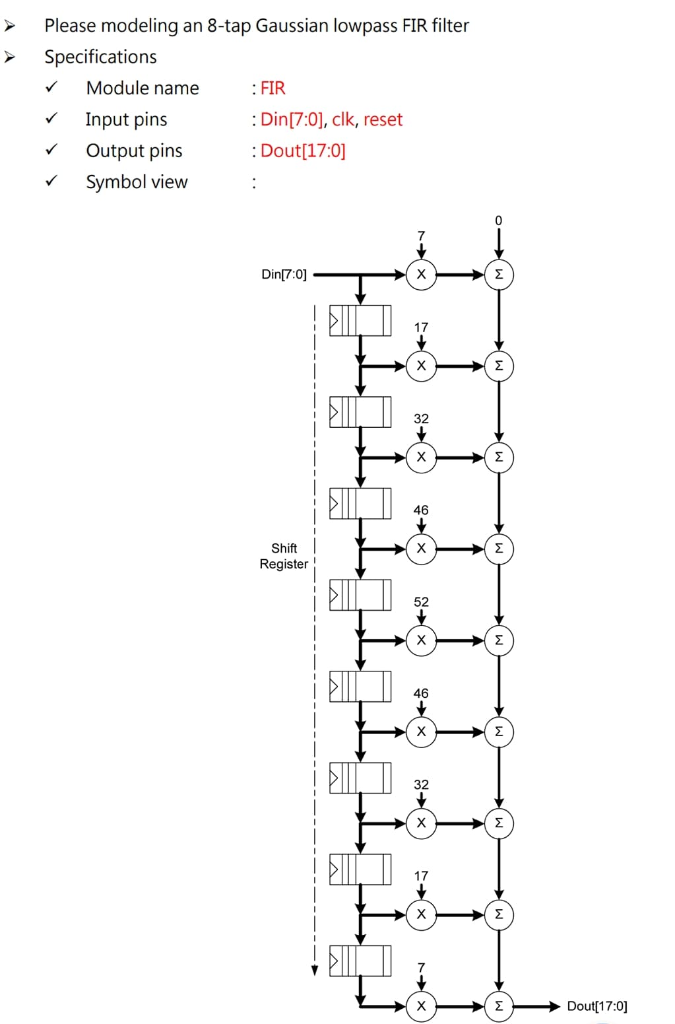

Low Pass FIR Filter verilog code.docx - Low Pass FIR Filter verilog code In this implementation we are using the same coefficients which we have used in | Course Hero

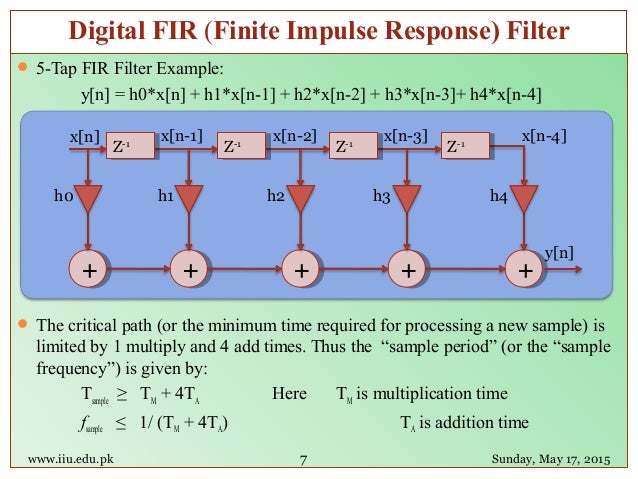

How to accelerate a simple, 16-bit, 12-tap DSP FIR filter by compiling it into FPGA hardware - Signal Processing Design

Efficient FPGA-based FIR – architecture and its significance in ultrasonic signal processing | JVE Journals

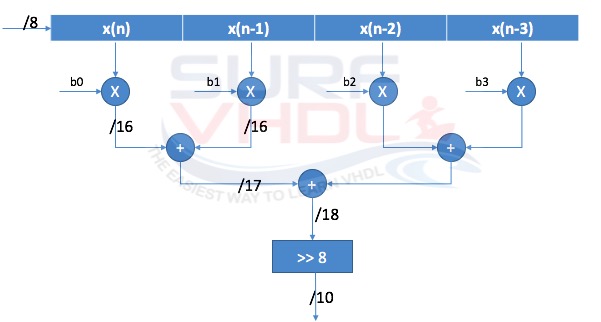

![Direct form 3-tap FIR Filter [1]. | Download Scientific Diagram Direct form 3-tap FIR Filter [1]. | Download Scientific Diagram](https://www.researchgate.net/profile/Manoj-Kumar-163/publication/335542128/figure/fig2/AS:798551772766214@1567400987804/Direct-form-3-tap-FIR-Filter-1.jpg)